# Analog Devices Welcomes Hittite Microwave Corporation

NO CONTENT ON THE ATTACHED DOCUMENT HAS CHANGED

### Typical Applications

The HMC990LP4E is Ideal for:

- Multiband/Multi-standard Cellular BTS Diversity Receivers

- GSM & 3G & LTE/WiMAX/4G

- MIMO Infrastructure Receivers

- Wideband Radio Receivers

- Multiband Basestations & Repeaters

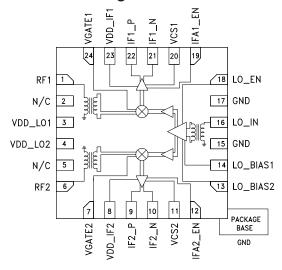

#### **Functional Diagram**

#### **Features**

Broadband Operation with no external matching Industry's Most Compact Solution, 4x4 mm<sup>2</sup> QFN Package

High-side and Low-side LO injection Operation

Wide IF Frequency Range

High Input IP3 of +25.6dBm @ 2200 MHz

Power Conversion Gain of 7.9 dB

Input P1dB of 12 dBm

SSB Noise Figure of 9 dB

55 dBc Channel-to-Channel Isolation

Dedicated Enable Pins for IF & LO amplifiers

Single-ended RF & LO input ports

#### **General Description**

The HMC990LP4E is a high linearity, dual channel down-converting mixer optimized for multi-standard diversity receiver applications that require low power consumption and small size. The HMC990LP4E features new wideband limiting LO amplifiers to achieve an unprecedented RF bandwidth of 700 MHz to 3500 MHz. Unlike conventional narrow-band downconverter RFICs, the HMC990LP4E supports both high-side and low-side LO injection over the entire RF frequency band. The RF and LO input ports are internally matched to  $50\Omega$ .

The HMC990LP4E integrates LO and IF amplifiers with enable functions, LO and RF baluns and high linearity passive mixer cores with bias control interface. The balanced passive mixer combined with high-linearity IF amplifier architecture of HMC990LP4E provides excellent LO-to-RF, LO-to-IF, and RF-to-IF isolations. The HMC990LP4E provides a very low noise figure of 9dB, and high IIP3 of +25.6dBm allowing device to be used in demanding wideband applications. The HMC990LP4E's input IP3 can be further improved by external matching for narrow-band applications. The HMC990LP4E has typical less than 1.5W power consumption which can be optimized through external bias control pins. The HMC990LP4E also features a very fast enable control interface for to be used for power saving in Time Division Duplex (TDD) applications. The HMC990LP4E is housed in a RoHS compliant 4x4 mm2 leadless QFN package.

Electrical Specifications,  $T_A$  = +25 °C, IF Frequency = 150 MHz, LO Power = 0 dBm, RF Input Power = -5dBm (-5 dBm / Tone for 2-Tone IP3 Tests,  $\Delta f$  = 1MHz), VDD\_LO1,2 = 3.3V, VDD\_IF<sup>[3]</sup>, VDD\_IF1,2 = 5V

| Parameter                      |               | Typical                                                                                                       |          |          |     |  |  |

|--------------------------------|---------------|---------------------------------------------------------------------------------------------------------------|----------|----------|-----|--|--|

| RF Input Frequency Range       |               | 700 -                                                                                                         | 3500     |          | MHz |  |  |

| LO Input Frequency Range       |               | 600 -                                                                                                         | 3800     |          | MHz |  |  |

| IF Output Frequency Range [10] |               | 10 - 470                                                                                                      |          |          |     |  |  |

|                                | RF=900 MHz[1] | RF=900 MHz <sup>[1]</sup> RF=1900 MHz <sup>[2][9]</sup> RF=2200 MHz <sup>[2]</sup> RF=2700 MHz <sup>[2]</sup> |          |          |     |  |  |

| Parameter                      | Тур.          | Тур. Тур. Тур. Тур.                                                                                           |          |          |     |  |  |

| Conversion Gain [8]            | 8.7           | 7.9                                                                                                           | 7.3      | 6.9      | dB  |  |  |

| IP3 (Input)                    | 25.1          | 25.0                                                                                                          | 25.6     | 24.3     | dBm |  |  |

| Noise Figure (SSB)             | 8.9           | 9.3                                                                                                           | 10.0     | 10.3     | dB  |  |  |

| 1 dB Compression (Input)       | 11.2          | 12.0                                                                                                          | 12.0     | 12.3     | dBm |  |  |

| LO leakage @ RF port           | -53           | -52                                                                                                           | -51      | -60      | dBm |  |  |

| RF to IF Isolation             | 45            | 41                                                                                                            | 42       | 42       | dB  |  |  |

| LO Input Return Loss           | -12           | -13                                                                                                           | -12      | -11      | dB  |  |  |

| RF Input Return Loss           | -11           | -13                                                                                                           | -15      | -17      | dB  |  |  |

| IF Input Return Loss           | -12           | -12                                                                                                           | -12      | -12      | dB  |  |  |

| Channel to Channel Isolation   | 62            | 53                                                                                                            | 52       | 52       | dBc |  |  |

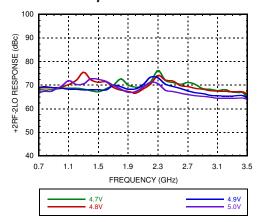

| +2RF-2LO Response              | 69            | 68                                                                                                            | 71       | 69       | dBc |  |  |

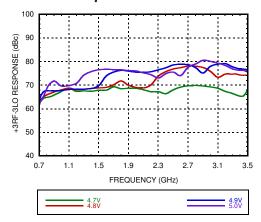

| +3RF-3LO Response              | 70            | 70                                                                                                            | 72       | 78       | dBc |  |  |

| LO Input Drive Level           | -6 to +3      | -6 to +3                                                                                                      | -6 to +3 | -6 to +3 | dBm |  |  |

| LO to IF Isolation [11]        | -38           | -38                                                                                                           | -38      | -38      | dBc |  |  |

### Typical RF Narrow Band Matching Performance

See Application Section for Further Details

| Parameter                    | Тур.        | Units |

|------------------------------|-------------|-------|

| Frequency Range              | 1850 - 2050 | MHz   |

| Conversion Gain              | 7.9         | dB    |

| IIP3                         | 25          | dBm   |

| NF (SSB)                     | 9.3         | dB    |

| IP1dB                        | 12          | dBm   |

| RF to IF Isolation           | 41          | dB    |

| Channel to Channel Isolation | 53          | dBc   |

| LO Input Drive Level         | -6 to +3    | dBm   |

### DC Power Supply Specifications,

| Parameter                                                             | Conditions                                        | Min.  | Тур. | Max.  | Units. |

|-----------------------------------------------------------------------|---------------------------------------------------|-------|------|-------|--------|

| IF Supply Voltage (VDD_IF <sup>[3]</sup> , VDD_IF1,2 <sup>[4]</sup> ) |                                                   | +4.75 | +5   | +5.25 | V      |

| LO Supply Volltage (VDD_LO1,2)                                        |                                                   | +3.15 | +3.3 | +3.45 | V      |

| IF Amplifier Supply Current when enabled                              | VDD_IF <sup>[3]</sup>                             |       | 148  |       | mA     |

|                                                                       | VDD_IF1 <sup>[4]</sup> + VDD_IF2 <sup>[4]</sup>   |       | 24   |       | mA     |

|                                                                       | VCS1 <sup>[5]</sup> + VCS2 <sup>[5]</sup>         |       | 3    |       | mA     |

|                                                                       | VDD_IF <sup>[3]</sup>                             |       | 0    |       | mA     |

| IF Amplifier Supply Current when disabled                             | VDD_IF1 <sup>[4]</sup> + VDD_IF2 <sup>[4]</sup>   |       | 3    |       | mA     |

|                                                                       | VCS1 <sup>[5]</sup> + VCS2 <sup>[5]</sup>         |       | 4    |       | mA     |

| 10.4 15 0 1 0 1 1                                                     | VDD_LO1,2                                         |       | 170  |       | mA     |

| LO Amplifier Supply Current when enabled                              | LO_BIAS1 <sup>[6]</sup> + LO_BIAS2 <sup>[6]</sup> |       | 4.6  |       | mA     |

| 104 15 0 10 1 1 15 11 1                                               | VDD_LO1,2                                         |       | 4    |       | mA     |

| LO Amplifier Supply Current when disabled                             | LO_BIAS1 <sup>[6]</sup> + LO_BIAS2 <sup>[6]</sup> |       | 5.4  |       | mA     |

| Vgate Bias when enabled                                               | VGATE1 + VGATE2                                   |       | 3.6  |       | mA     |

| Vgate Bias when disabled                                              | VGATE1 + VGATE2                                   |       | 2    |       | mA     |

### LO/IF, Enable/Disable Interface Specifications,

| Parameter Conditions                                          |                                 | Min. | Тур. | Max. | Units. |

|---------------------------------------------------------------|---------------------------------|------|------|------|--------|

| LO_EN High Level                                              | LO Amplifier Disabled           | +3   | +5   |      | V      |

| LO_EN Low Level LO Amplifier Enabled                          |                                 | 0    | 0    | +1   | V      |

| IFA1_EN / IFA2_EN High Level Channel1/2 IF Amplifier Disabled |                                 | +3   | +5   | 5    | V      |

| IFA1_EN / IFA2_EN Low Level                                   | Channel1/2 IF Amplifier Enabled | 0    | 0    | +1   | V      |

| Enable Settling Time[7]                                       |                                 |      | 30   |      | ns     |

| Disable Settling Time <sup>[7]</sup>                          |                                 |      | 130  |      | ns     |

<sup>[1]</sup> High side LO injection, VGATE1,2 = 5.0V [2] Low side LO injection, VGATE1,2 = 4.8V

<sup>[3]</sup> Supply voltage for IF amplifiers through choke inductors. See application circuit.

<sup>[4]</sup> Supply voltage for bias circuit of IF amplifiers. See application circuit.

<sup>[5]</sup> Bias Control pins for IF amplifiers. See application circuit.

<sup>[6]</sup> Bias Control pins for LO amplifier. See application circuit.

<sup>[7]</sup> Remove bypass capacitors on LO\_EN and IFA1,2\_EN pins for given settling times. See application circuit. [8] Balun losses at IF output port are de-embedded.

<sup>[9] 1900</sup> MHz matching band covers 1850 - 2050 MHz

<sup>[10]</sup> The part is characterized with IF = 150 MHz. External matching maybe needed for diffrent IF frequencies.

<sup>[11]</sup> LO Power is 0 dBm, RF Power is -5 dBm.

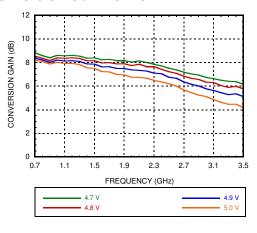

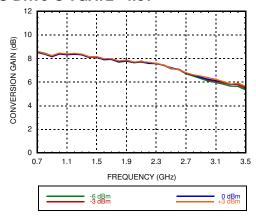

#### Conversion Gain vs. VGATE[1]

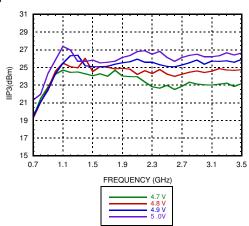

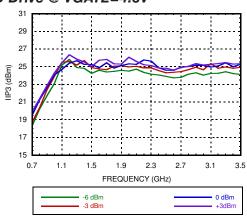

#### Input IP3 vs. VGATE[1]

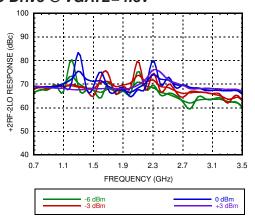

#### +2RF -2LO Response vs. VGATE[1]

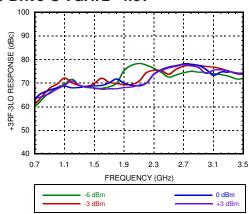

+3RF -3LO Response vs. VGATE[1]

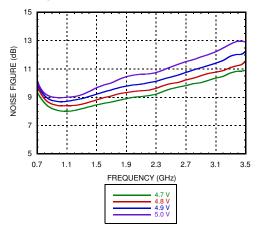

### Noise Figure vs. VGATE[1]

[1] VGATE is bias voltage for passive mixer cores (VGATE1 and VGATE2 pins). Refer to pin description table. All plots are for Low Side LO injection unless otherwise noted. Balun losses at IF output ports are de-embedded.

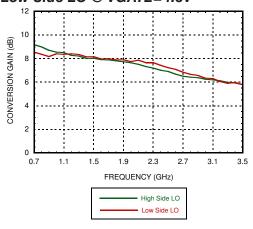

### Conversion Gain vs. High Side LO & Low Side LO @ VGATE=4.8V

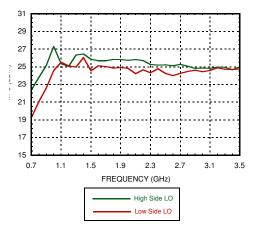

### Input IP3 vs. High Side LO & Low Side LO @ VGATE=4.8V

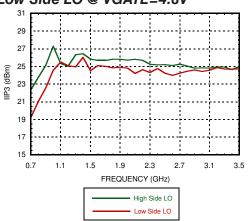

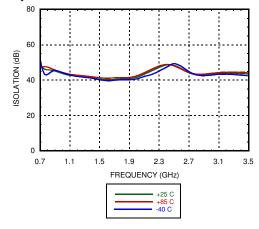

### RF/IF Isolation vs. Temperature @ VGATE=4.8V

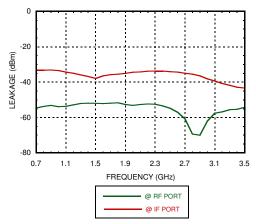

### LO Leakage @ VGATE=4.8V

### Conversion Gain vs. LO Drive @ VGATE=4.8V

### Input IP3 vs. LO Drive @ VGATE=4.8V

+2RF -2LO Response vs. LO Drive @ VGATE=4.8V

+3RF -3LO Response vs. LO Drive @ VGATE=4.8V

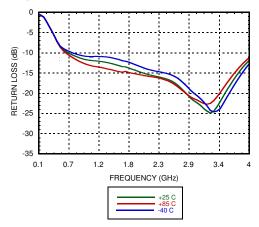

RF Input Return Loss @ VGATE=4.8V [1]

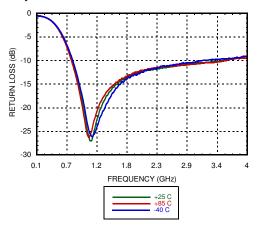

LO Input Return Loss @ VGATE=4.8V

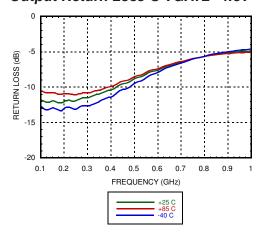

IF Output Return Loss @ VGATE=4.8V [1]

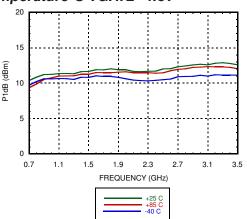

Input P1dB vs.

Temperature @ VGATE=4.8V

[1] LO input Frequency = 1500MHz, LO power = 0 dBm.

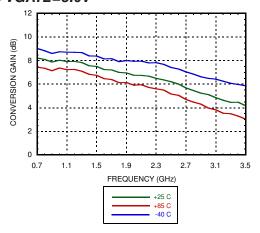

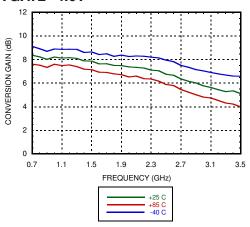

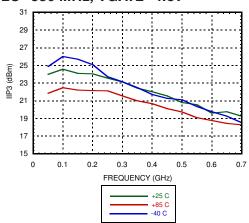

### Conversion Gain vs. Temperature @ VGATE=5.0V

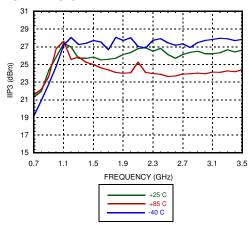

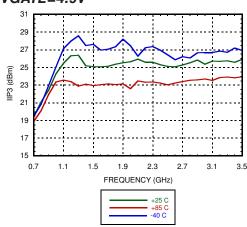

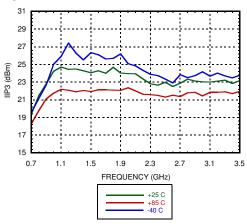

### Input IP3 vs. Temperature @ VGATE=5.0V

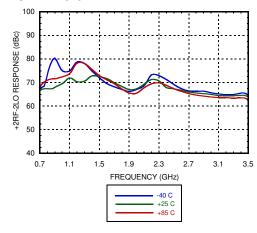

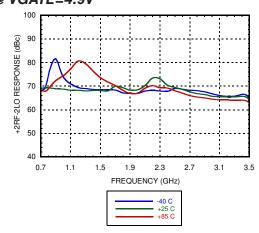

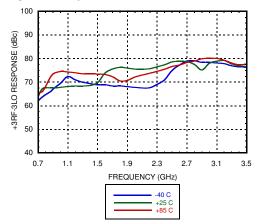

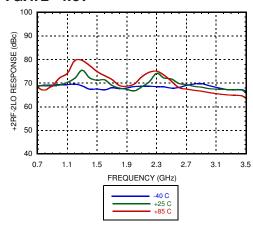

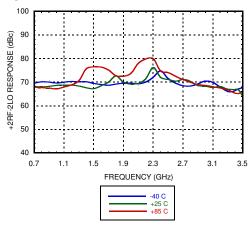

### +2RF -2LO Response vs. Temperature @ VGATE=5.0V

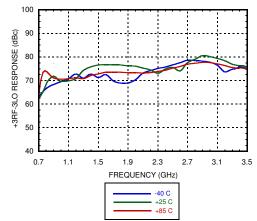

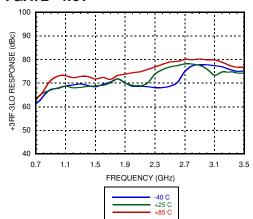

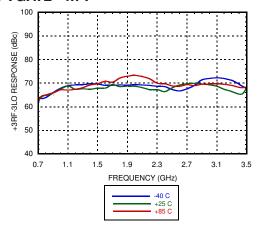

+3RF -3LO Response vs. Temperature @ VGATE=5.0V

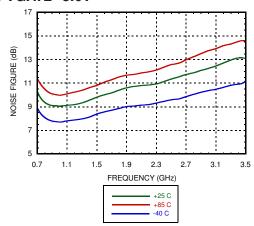

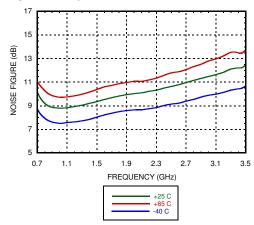

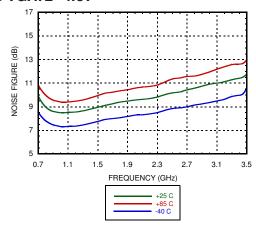

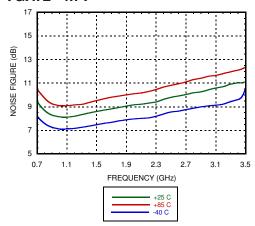

### Noise Figure vs. Temperature @ VGATE=5.0V

### Conversion Gain vs. Temperature @ VGATE=4.9V

+2RF -2LO Response vs. Temperature @ VGATE=4.9V

Input IP3 vs. Temperature @ VGATE=4.9V

+3RF -3LO Response vs. Temperature @ VGATE=4.9V

Noise Figure vs. Temperature @ VGATE=4.9V

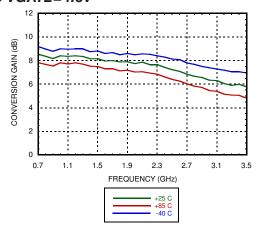

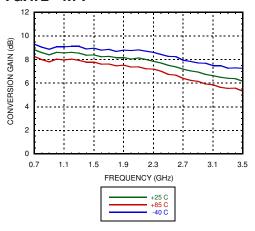

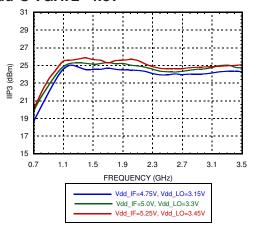

### Conversion Gain vs. Temperature @ VGATE=4.8V

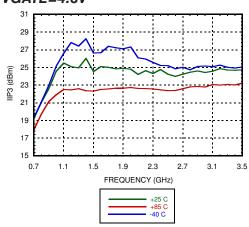

Input IP3 vs. Temperature @ VGATE=4.8V

### +2RF -2LO Response vs. Temperature @ VGATE=4.8V

+3RF -3LO Response vs. Temperature @ VGATE=4.8V

### Noise Figure vs. Temperature @ VGATE=4.8V

### Conversion Gain vs. Temperature @ VGATE=4.7V

@ VGATE=4.7V

Input IP3 vs. Temperature

### +2RF -2LO Response vs. Temperature @ VGATE=4.7V

+3RF -3LO Response vs. Temperature @ VGATE=4.7V

### Noise Figure vs. Temperature @ VGATE=4.7V

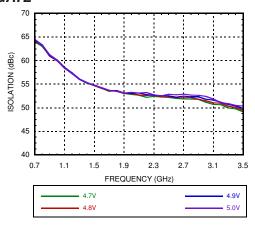

### Channel to Channel Isolation vs. VGATE

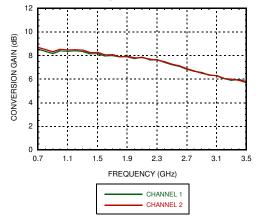

### Conversion Gain, Channel Matching @ VGATE=4.8V

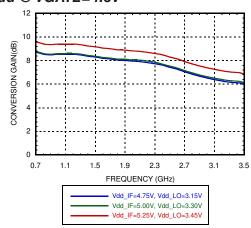

### Conversion Gain vs. Vdd @ VGATE=4.8V

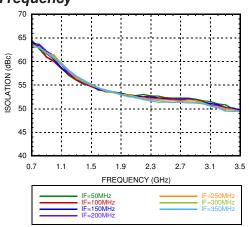

### Channel to Channel Isolation vs. IF Frequency

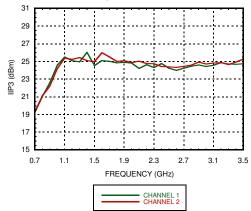

### Input IP3, Channel Matching @ VGATE=4.8V

### Input IP3 vs. Vdd @ VGATE=4.8V

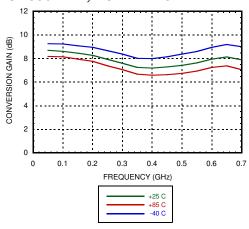

### Conversion Gain vs. IF Frequency @ LO=850 MHz, VGATE=4.8V

### Conversion Gain vs. IF Frequency @ LO=1800 MHz, VGATE=4.8V

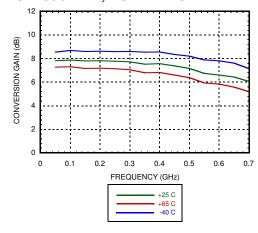

### IIP3 vs. IF Frequency @ LO=850 MHz, VGATE=4.8V

### IIP3 vs. IF Frequency @ LO=1800 MHz, VGATE=4.8V

### Harmonics of LO

|                | nLO Spur @ RF Port |     |     |     |  |  |

|----------------|--------------------|-----|-----|-----|--|--|

| LO Freq. (GHz) | 1                  | 2   | 3   | 4   |  |  |

| 0.7            | -55                | -48 | -65 | -64 |  |  |

| 1.1            | -53                | -50 | -65 | -54 |  |  |

| 1.5            | -53                | -52 | -66 | -54 |  |  |

| 1.9            | -53                | -49 | -70 | -64 |  |  |

| 2.3            | -54                | -48 | -68 | -51 |  |  |

| 2.7            | -72                | -46 | -59 | -48 |  |  |

| 3.1            | -54                | -51 | -73 | -48 |  |  |

| 3.5            | -59                | -63 | -59 | -46 |  |  |

| LO = 0dBm      |                    |     |     |     |  |  |

### **MxN Spurious @ IF Port**

|     | nLO  |      |      |      |      |  |

|-----|------|------|------|------|------|--|

| mRF | 0    | 1    | 2    | 3    | 4    |  |

| 0   | xx   | -39  | -56  | -50  | -46  |  |

| 1   | -44  | 0    | -40  | -19  | -50  |  |

| 2   | -66  | -53  | -60  | -58  | -76  |  |

| 3   | -100 | -59  | -92  | -66  | -100 |  |

| 4   | -113 | -107 | -112 | -109 | -110 |  |

RF Freq. = 0.9 GHz @-5 dBm

LO Freq. = 0.8 GHz @ 0 dBm

All values in dBc below IF power level (1RF - 1LO).

### **MxN Spurious @ IF Port**

All values in dBm measured at RF port.

|     | nLO  |      |      |      |      |  |  |

|-----|------|------|------|------|------|--|--|

| mRF | 0    | 1    | 2    | 3    | 4    |  |  |

| 0   | xx   | -38  | -37  | -60  | -49  |  |  |

| 1   | -50  | 0    | -44  | -35  | -73  |  |  |

| 2   | -70  | -56  | -66  | -64  | -84  |  |  |

| 3   | -114 | -75  | -97  | -66  | -108 |  |  |

| 4   | -123 | -132 | -125 | -111 | -117 |  |  |

RF Freq. = 1.9 GHz @-5 dBm LO Freq. = 1.8 GHz @ 0 dBm

All values in dBc below IF power level (1RF - 1LO).

### **MxN Spurious @ IF Port**

|     |      | nLO  |      |      |      |  |  |

|-----|------|------|------|------|------|--|--|

| mRF | 0    | 1    | 2    | 3    | 4    |  |  |

| 0   | xx   | -38  | -39  | -63  | -45  |  |  |

| 1   | -54  | 0    | -45  | -45  | -71  |  |  |

| 2   | -70  | -81  | -68  | -78  | -94  |  |  |

| 3   | -121 | -87  | -102 | -69  | -100 |  |  |

| 4   | -123 | -138 | -123 | -142 | -117 |  |  |

RF Freq. = 2.5 GHz @-5 dBm

LO Freq. = 2.4 GHz @ 0 dBm

All values in dBc below IF power level (1RF - 1LO).

### Typical Supply Current vs. Vdd

| VDD_IF<br>VDD_IF1<br>VDD_IF2<br>(V) | Idd_IF<br>(mA) | VDD_LO1,<br>VDD_LO2<br>(V) | Idd_LO<br>(mA) |

|-------------------------------------|----------------|----------------------------|----------------|

| 4.75                                | 162            | 3.15                       | 177            |

| 5.00                                | 180            | 3.30                       | 170            |

| 5.25                                | 198            | 3.45                       | 181            |

#### **Truth Table**

| IFA1_EN<br>(V) | IFAMP1 | IFA2_EN<br>(V) | IFAMP2 | LO_EN<br>(V) | LO_STAGES |

|----------------|--------|----------------|--------|--------------|-----------|

| Low            | ON     | Low            | ON     | Low          | ON        |

| High           | OFF    | High           | OFF    | High         | OFF       |

### **Absolute Maximum Ratings**

| RF Input Power (VDD_IF= +5V, VDD_LO1,2=3.3V)                   | +20 dBm       |

|----------------------------------------------------------------|---------------|

| LO Input Power (VDD_IF= +5V, VDD_LO1,2=3.3V)                   | +20 dBm       |

| VDD_IF, VDD_LO1,2                                              | 6V            |

| VGATE1,2                                                       | 5.5V          |

| Max. Channel Temperature                                       | 175°C         |

| Continuous Pdiss (T = 85°C)<br>(derate 77.63 mW/°C above 85°C) | 5.05 W        |

| Thermal Resistance (channel to ground paddle)                  | 12.8 °C/W     |

| Storage Temperature                                            | -65 to 150°C  |

| Operating Temperature                                          | -40 to +85 °C |

| ESD Sensitivity (HBM)                                          | Class 1B      |

### **Recommended Operating Conditions**

| Parameter            | Min. | Тур. | Max. | Units |  |  |  |

|----------------------|------|------|------|-------|--|--|--|

| Temperature          |      |      |      |       |  |  |  |

| Junction Temperature |      |      | 150  | °C    |  |  |  |

| Ambient Temperature  | -40  |      | 85   | °C    |  |  |  |

### **Outline Drawing**

### BOTTOM VIEW PIN 24 — .016 [0.40] REF .008 [0.20] MIN PIN 1 H990 XXXX61 53 13 **EXPOSED** LOT NUMBER .116 2.95 2.65 GROUND **PADDLE** SQUARE 0.05 SEATING

PLANE

-C-

- 1. PACKAGE BODY MATERIAL: LOW STRESS INJECTION MOLDED PLASTIC SILICA AND SILICON IMPREGNATED.

- 2. LEAD AND GROUND PADDLE MATERIAL: COPPER ALLOY.

- 3. LEAD AND GROUND PADDLE PLATING: 100% MATTE TIN

- 4. DIMENSIONS ARE IN INCHES [MILLIMETERS].

- 5. LEAD SPACING TOLERANCE IS NON-CUMULATIVE.

- 6. CHARACTERS TO BE HELVETICA MEDIUM, .025 HIGH, WHITE INK, OR LASER MARK LOCATED APPROX. AS SHOWN.

- 7. PAD BURR LENGTH SHALL BE 0.15mm MAX. PAD BURR HEIGHT SHALL BE 0.05mm MAX.

- 8. PACKAGE WARP SHALL NOT EXCEED 0.05mm

- 9. ALL GROUND LEADS AND GROUND PADDLE MUST BE SOLDERED TO PCB RF GROUND.

- 10. REFER TO HITTITE APPLICATION NOTE FOR SUGGESTED PCB LAND PATTERN.

#### Package Information

.003[0.08] C

| . ackage information |                                                    |               |            |                    |  |  |

|----------------------|----------------------------------------------------|---------------|------------|--------------------|--|--|

| Part Number          | Package Body Material                              | Lead Finish   | MSL Rating | Package Marking    |  |  |

| HMC990LP4E           | RoHS-compliant Low Stress Injection Molded Plastic | 100% matte Sn | MSL1 [1]   | <u>H990</u><br>XXX |  |  |

<sup>[1]</sup> Max peak reflow temperature of 260 °C

<sup>[2] 4-</sup>Digit lot number XXXX

### **Pin Descriptions**

| Pin Number | Function            | Description                                                                                                                                                                       | Interface Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1, 6       | RF1, RF2            | RF input pins of the mixer, internally matched to 50 Ohms. RF input pins require off_chip DC blocking capacitors. See application circuit.                                        | RF1 CENTER OF THE PROPERTY OF |  |  |

| 2,5        | N/C                 | Not connected internally.                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

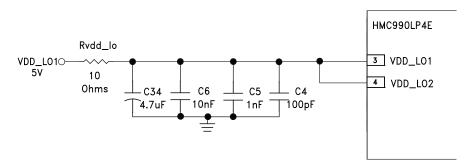

| 3,4        | VDD_LO1,<br>VDD_LO2 | 3.3V bias supply for LO Drive stages. Refer to application circuit for appropriate filtering.                                                                                     | VDD_LO1 OVDD_LO2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 7          | VGATE2              |                                                                                                                                                                                   | VGATE1 OF ESD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 24         | VGATE1              | Bias pins for mixer cores. Set from 4.7V to 5.0V for operating frequency band.                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 8          | VDD_IF2             | Supply voltage pins for IF amplifiers' bias circuits.                                                                                                                             | VDD_IF1<br>VDD_IF2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 23         | VDD_IF1             | Connect to 5V supply through filtering.                                                                                                                                           | ESD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 9          | IF2_P               |                                                                                                                                                                                   | IF1P IF1N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 10         | IF2_N               | Differential IF outputs.Connect to 5V supply through choke inductors. See application circuit.                                                                                    | IF1P O IF1N IF2N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 21         | IF1_N               |                                                                                                                                                                                   | ESD ESD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 22         | IF1_P               |                                                                                                                                                                                   | 물 물                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 11,20      | VCS2,VCS1           | Bias control pins for IF amplifiers. Connect to 5V supply through 130 Ohms resistors. Refer to application section for proper values of resistors to adjust IF amplifier current. | VCS1<br>VCS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

### Pin Descriptions (continued)

| Pin Number | Function              | Description                                                                                                                                                                       | Interface Schematic     |

|------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| 12,19      | IFA2_EN,<br>IFA1_EN   | Enable pins for IF Amplifiers. When connected to LOW or left unconnected, amplifiers are enabled. For disable mode connect to HIGH.                                               | IF1_EN IF2_EN ESD       |

| 13,14      | LO_BIAS2,<br>LO_BIAS1 | Bias control pins for LO Amplifiers. Connect to 5V supply through 150 Ohms resistors. Refer to application section for proper volues of resistors to adjust LO amplifier current. | LO_BIAS1 LO_BIAS2 ESD = |

| 15,17      | GND                   | Connect to RF and DC ground.                                                                                                                                                      | GND                     |

| 16         | LO_IN                 | LO input of the mixer. Internally matched to 50 Ohms.  Requires off_chip DC blocking capacitor.  See application circuit.                                                         | 70_IX                   |

| 18         | LO_EN                 | Enable for LO Amplifiers. When connected to LOW or<br>left unconnected, amplifiers are enabled.<br>For disable mode connect to HIGH.                                              | LO_EN O                 |

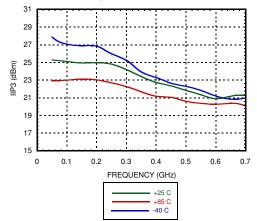

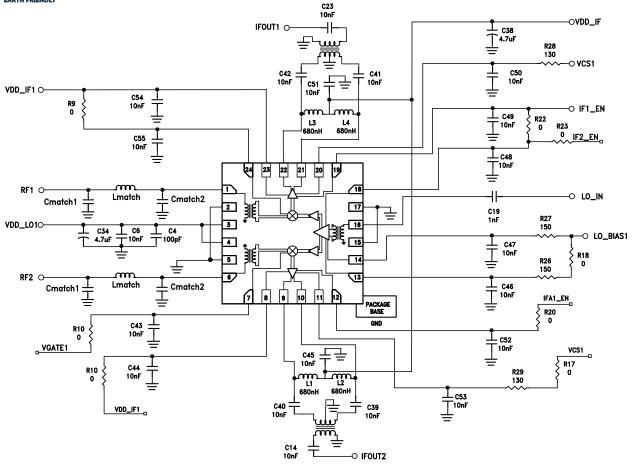

#### **Evaluation PCB**

#### List of Materials for Evaluation PCB EVAL01- HMC990LP4E [1]

| Item                                               | Description                    |

|----------------------------------------------------|--------------------------------|

| J1 - J5                                            | PCB Mount SMA Connector        |

| TP1,TP2,TP4,TP5,TP8,TP13,TP14                      | Test Point                     |

| L1-L4                                              | 680 nH Inductor, 0603 Pkg.     |

| C45-C47,C50-C51,C53-C55                            | 0.01 μF Capacitor, 0603 Pkg    |

| C34,C38                                            | 4.7 μF CaSE A, Tantalum        |

| C4                                                 | 100 pF Capacitor, 0402 Pkg.    |

| C2,C7,C19                                          | 1 nF Capacitor, 0402 Pkg.      |

| C6,C14,C23,C39-C44                                 | 10 nF Capacitor, 0402 Pkg.     |

| R2,R4-R6,R8,R9-R11,R14-R15,R17-R18,R20,R22,R23,R25 | 0 ohm Resistor, 0402 Pkg.      |

| R24                                                | 100 Kohm Resistor, 0402 Pkg.   |

| R26-R27                                            | 150 ohm Resistor, 0402 Pkg.    |

| R28-R29                                            | 130 ohm Resistor, 0402 Pkg.    |

| T1-T2                                              | 1:4 Transformer - ETC4-1T-7TR. |

[1] Reference this number when ordering complete evaluation PCB

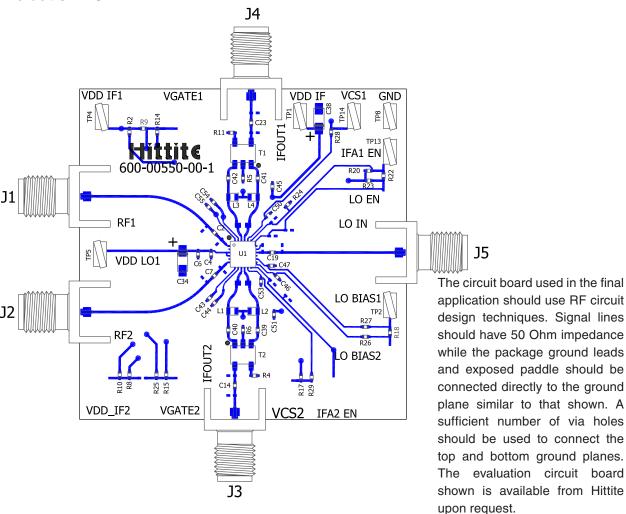

### **Application Circuit - Broadband**

#### Notes:

- 1-Differential IF output transmission lines should be symmetrical

- 2-Refer to evaluation PCB for component placements and distances

### **Application Information**

The HMC990LP4E is a broadband dual channel, high dynamic range, high gain, low noise, high-linearity downconverting mixer designed for covering RF frequencies from 700 MHz to 3.5 GHz. The HMC990LP4E's low noise and high linearity performance makes it suitable for a wide range of transmission standards, including LTE, CDMA, GSM, MC-GSM, W-CDMA, UMTS, TD-SCDMA, WiMAX applications.

The HMC990LP4E offers an easy-to-use and complete frequency conversion solution for diversity and MIMO receiver applications in a highly compact 4x4 mm<sup>2</sup> QFN package. The HMC990LP4E greatly simplifies the design of diversity and MIMO receiver applications by increasing the integration level and reducing the number of required circuit elements thereby reducing cost, area, and power consumption.

### **Principle of Operation**

The HMC990LP4E has two identical, symmetrical double-balanced passive mixers. These mixers are driven from a common single-ended LO input that is broadband matched to 50  $\Omega$  and requires only a standard DC-blocking capacitor. The single-ended LO input is converted into differential through the on-chip integrated balun followed by a LO driver stage. The differential signal is divided into two differential paths and each mixer is driven by a separate LO amplifier.

The HMC990LP4E's single-ended RF inputs are converted into differential through the on-chip integrated baluns. The single-ended RF inputs are internally broadband matched to  $50~\Omega$  and require only standard DC-blocking capacitors. However, the HMC990LP4E's RF inputs can be externally matched for narrow band application frequency with a simple matching network including a series inductor and a shunt capacitor to further improve the performance. Please refer to the application circuit for narrowband RF input matching for the detailed information.

The HMC990LP4E's IF amplifiers are designed for differential 200  $\Omega$  output impedance. A few external components are required at these IF outputs for the broadband frequency response as recommended in the application circuit. Please refer to the IF output interface section for more information.

The HMC990LP4E requires 5V and 3.3V supply voltages and external bias voltages. Bias voltages generate reference currents for the IF and LO amplifiers. 3.3V supply voltage and the external bias voltages can be generated from 5V supply voltage to operate with a single supply. Please refer to the single supply operation section for more information.

The reference currents to the LO amplifiers and IF amplifiers can be disabled through LO\_EN and IFA1\_EN, IFA2\_EN pins respectively. If the EN pins are connected to LOW or left unconnected, the part operates normally. If the EN pins are connected to HIGH, the LO amplifiers and IF amplifiers are disabled.

### Single Supply Operation

The HMC990LP4E requires 5V and 3.3V supply voltages and the external bias voltages. The external bias voltages except VGATE1, VGATE2 pin voltages are already generated from 5V supply voltage on evaluation board (see application circuit). These bias voltages can be optimized by series resistances with appropriate values from the 5V supply to the bias pins (VCS1, VCS2, LO\_BIAS1, LO\_BIAS2). The resistor values on VCS1, VCS2 and LO\_BIAS1, LO\_BIAS2 traces on evaluation board are 130 Ohms and 150 Ohms respectively. Refer to the VCS Interface and LO\_BIAS Interface section for more information.

The nominal VGATE1, VGATE2 pin voltages are 4.8V that is applied externally. However VGATE1, VGATE2 pin voltages can be tuned between 4.7V and 5V for optimization of Input IP3 and conversion gain performances. After VGATE1, VGATE2 pin voltages are optimized, these pin voltages can be generated from 5V supply by changing the values of series resistors, R14 and R15. Refer to the VGATE interface section for more information.

The 3.3V supply voltage for the LO amplifiers can be generated from 5V supply voltage by adding 20 Ohms resistors between VDD\_LO1, VDD\_LO2 pins and 5V supply voltage. VDD\_LO1 and VDD\_LO2 pins are shorted and connected to VDD\_LO1 test point on evaluation board, hence a 10 Ohms resistor (Rvdd\_lo) can be added in series with VDD\_LO1 test point as shown in Figure 1. The resistor must have a power rating of 1/2W or more.

Figure 1. Interface to generate 3.3V for VDD\_LO1 and VDD\_LO2 pins from 5V Supply.

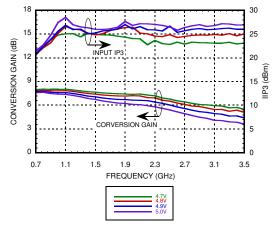

#### VGATE Interface

The VGATE1, VGATE2 pins are bias pins for mixer cores. The nominal VGATE1, VGATE2 pin voltages are 4.8V that is applied externally. However voltage can be tuned between 4.7V and 5V for optimizing input IP3 and conversion gain performances for desired frequency band. Higher IIP3 values can be obtained by increasing the VGATE1, VGATE2 pin voltages but this will reduce mixer's conversion gain. Figure-2 shows the measured conversion gain and IIP3 for four values of the VGATE1, VGATE2 pin voltages.

**Figure-2.** Conversion Gain & IIP3 vs. RF Frequency over VGATE Pin Voltage @25C, IF =100 MHz [1]

After the VGATE voltage is tuned for optimized IIP3 and conversion gain performance, the VGATE pin voltage can be generated from 5V supply voltage by changing the value of series resistors, R14 and R15 from 0 Ohm to an appropriate value.

Table-1 shows the typical resistor values that need to be added in series with VGATE1, VGATE2 pins for different VGATE voltages. A fine tune for R14 and R15 resistors can be needed if a better fit is required.

Table-1: Resistor values for different VGATE pin voltages

| TOATE pill Tollages |         |  |

|---------------------|---------|--|

| Vgate1=Vgate2       | R14=R15 |  |

| 4.7V                | 174 Ohm |  |

| 4.8V                | 120 Ohm |  |

| 4.9V                | 56 Ohm  |  |

| 5.0V                | 0 Ohm   |  |

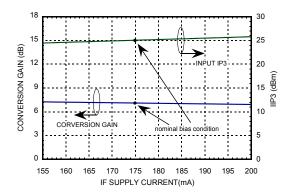

#### VCS Interface and LO BIAS Interface

The VCS1, VCS2 pins are bias pins for IF amplifiers on each channel and set the reference currents to these IF amplifiers. The VCS voltage is generated from the 5V supply by series resistances. Higher IIP3 values can be obtained by reducing the values of these series resistances R28 and R29, which will increase the total supply current of the IF amplifiers. Figure-3a shows the measured conversion gain and IIP3 vs. total supply current from the VDD\_IF1, VDD\_IF2 and VDD\_IF test points at 1900MHz.

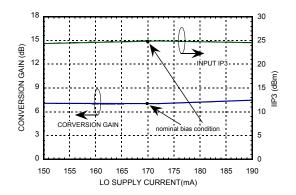

The LO\_BIAS1, LO\_BIAS2 pins are bias pins for LO amplifiers and set the reference currents to these LO amplifiers. The LO\_BIAS voltage is generated from the 5V supply by series resistances R26 and R27. Figure-3b shows the measured conversion gain and IIP3 vs. total supply current from the VDD\_LO1 test point at 1900MHz.

**Figure 3a.** IIP3 and conversion gain vs. IF stage's Total supply current @25C, RF=1900MHz, IF= 100MHZ, VGATE=4.8V [1]

**Figure 3b.** IIP3 and conversion gain vs. LO stage's Total supply current @25C, RF=1900MHz, IF= 100MHZ, VGATE=4.8V [1]

Table-2 and Table-3 show the typical resistor values that are used in series with VCS1, VCS2 and LO\_BIAS1, LO\_BIAS2 pins for different total supply current values of IF and LO stages. A fine tune for these resistors can be needed if a better fit is required.

Table-2: Resistor values for total supply current of IF Amplifiers

| IF Amplifiers Total Supply Current | R28=R29 |

|------------------------------------|---------|

| 155mA                              | 820 Ohm |

| 180mA                              | 590 Ohm |

| 200mA                              | 390 Ohm |

Table-3: Resistor values for total supply current of LO Amplifier

| LO Amplifier Total Supply Current | R26=R27 |

|-----------------------------------|---------|

| 150mA                             | 620Ohm  |

| 170mA                             | 270 Ohm |

| 190mA                             | 0 Ohm   |

#### External RF Matching

The HMC990LP4E's RF inputs are internally broadband matched to  $50\Omega$ . RF inputs can be externally matched for a specific RF frequency band of interest to further improve Input IP3 (IIP3). Matching RF inputs to a specific RF frequency band can be easily accomplished by adding a series inductor and a shunt capacitor. See Table-4 for values of the external matching components for corresponding RF frequency bands. Figure-4 shows the application circuit with the external components on RF input pins.

LO\_BIAS2 and VGATE1, VGATE2 pin voltages can be optimized for a specific RF frequency band by changing the resistor values in series with these pins. Table-1 shows the resistor values (R14, R15) for corresponding VGATE pin voltage. Table-4 shows the resistor value (R26) for recommended LO\_BIAS2 pin voltage.

Figure-5 shows the measured conversion gain and IIP3 for 900MHz,1900MHz and 2500MHz RF frequency bands.

Table-4: Components for Selected Frequency Bands

| Tune Option | Lmatch | Cmatch1, | Cmatch2 | R26      | Recommended VGATE1,2<br>Voltages |

|-------------|--------|----------|---------|----------|----------------------------------|

| 900 MHz     | 6.8nH  | 2.7pF    | Open    | 150 Ohms | 5.0V                             |

| 1900 MHz    | 2.7nH  | 1pF      | Open    | 270 Ohms | 4.8V                             |

| 2500MHz     | 1nH    | Open     | 1pF     | 270 Ohms | 4.8V                             |

## RoHS V

### BROADBAND HIGH IP3 DUAL CHANNEL DOWNCONVERTER, 0.7 - 3.5 GHz

Figure-4. Application Circuit for Narrowband RF Input Matching

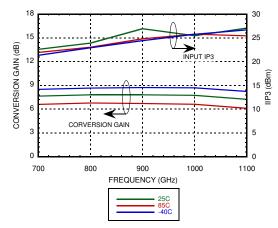

Figure-5a. IIP3 and Conversion Gain with matching for 900 MHz band

VGATE=5.0 V, IF=100 MHz [1]

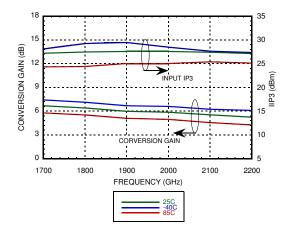

Figure-5b. IIP3 and Conversion Gain with matching for 1900 MHz band

VGATE=4.8 V, IF=100 MHz [1]

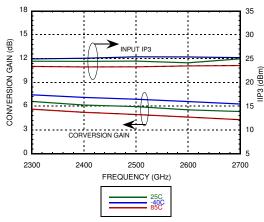

Figure-5c. IIP3 and Conversion Gain with matching for 2500 MHz bandVGATE=4.8 V, IF=100 MHz [1]

It is recommended to use high side LO injection for RF frequencies below 1GHz for better IIP3. For instance, higher IIP3 can be obtained if LO input is driven with high side at RF=900 MHz. Please refer to Figure-6.

Figure-6. Input IP3 vs. High Side LO & Low Side LO @ VGATE=4.8V

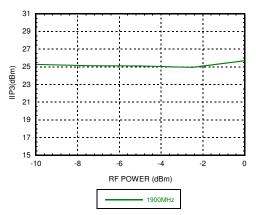

### Input IP3 Dependence on RF Input Power

The HMC990LP4E accepts a wide range of RF input power. Figure-7 shows the IIP3 vs. RF input power for 1900 MHz RF and 150 MHz IF.

Figure-7. IIP3 vs. RF Input Power, RF=1900MHz, IF=150MHz, VGATE=4.8V

[1] Balun losses at IF output ports are de-embedded.

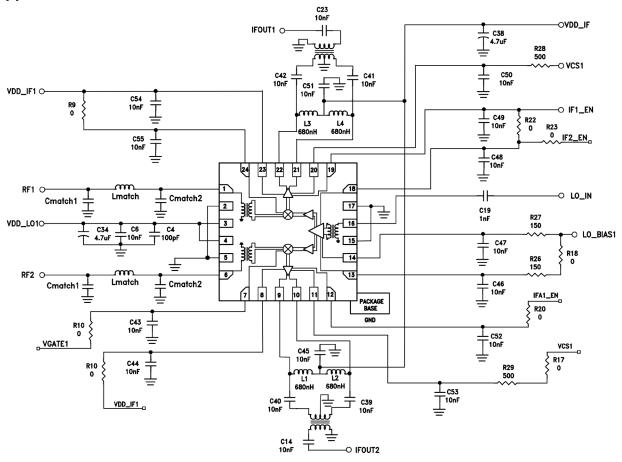

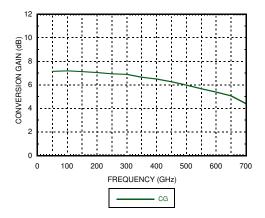

### IF Output Interface

The HMC990LP4E's differential IF output pins are biased at the 5V supply voltage through choke inductors as shown in the application circuit. The default values of these choke inductors are 680nH. Figure-8 shows the measured conversion gain vs. IF frequency where 1-dB IF bandwidth is around 470MHz and 3-dB IF bandwidth is above 700MHz. Higher IF bandwidth values can be obtained by reducing the value of the choke inductors.

The baluns at the IF outputs are used to convert the 200 Ohms differential output impedance of HMC990LP4E to single-ended 50 Ohms for characterization.

Figure-8. Conversion gain vs. IF Frequency @ LO=1.5GHz [1]